In an NMOS, does current flow from source to drain or vice-versa?

9 with NMOS, current flows from Drain-to-source (arrow points away from device at the Source) with PMOS, current flows from Source-to-drain (arrow points to the device at the Source) P-channel …

Why choose a PMOS over an NMOS or vice versa?

Sep 1, 2019 · First and foremost, A PMOS is a "backwards" NMOS (and visa-versa). In an NMOS, in typical operation current flows from drain to source when the gate voltage is higher than the source …

transistors - How to set up NMOS and PMOS for a simulation ...

Apr 23, 2025 · We have a lab about transistors, and we're using Virtuoso. I'm supposed to build a testbench for NMOS and PMOS, and for each of those, I need to decide where to connect either of …

ltspice - How to do NMOS modeling analysis in Spice - Electrical ...

Jan 29, 2022 · Here is my circuit in Spice: I want to do a simple analysis of the NMOS like this: What kind of command should I use?

Benefits/downside of discrete high-/low-side NMOS/PMOS and high …

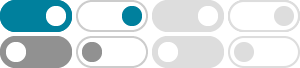

Feb 28, 2023 · Low-side NMOS High-side NMOS Low-side PMOS High-side PMOS Boot-strap NMOS circuit The basic functionality of those circuits is rather the same. #3 doesn't make that much sense …

Why is the PMOS in NAND gate in Parallel and NMOS Series?

Aug 17, 2020 · The changing from NMOS to PMOS automatically takes care of the inverted inputs because that is the nature of PMOS and NMOS, so all you have to do is change the series …

mosfet - High-side NMOS for buck converter? - Electrical Engineering ...

Jun 14, 2021 · In an actual device using NMOS high-side FETs there's a trick to dealing with this issue: use a bootstrap voltage generator to make the high-side gate driver supply.

Transconductance of a nmos transistor - Electrical Engineering Stack ...

May 13, 2017 · Can anyone explain me how I can find gm from this schematic below (for a nmos transistor)when VGS=6V and VDS=6V?

Understanding the working of a NAND GATE using NMOS Transistors

May 22, 2020 · Here is the NMOS for a NAND GATE, where Z indicates that it's in a floating state, the bold blue line indicates that the source-drain is set to High, the bold black line indicates that the …

Biasing common-source NMOS with active load and fixed Vgs

Nov 24, 2024 · I came across this circuit, a common-source NMOS amplifier with PMOS current mirror as active load AND a fixed DC voltage level at the NMOS gate. Since we're using a current mirror, …